# Multi-Level Amplitude Modulation of a 16.8-GHz Class-E Power Amplifier With Negative Resistance Enhanced Power Gain for 400-Mbps Data Transmission

Hsin-Ta Wu, Ruonan Han, Wuttichai Lerdsitsomboon, Changhua Cao, and Kenneth K. O

Abstract—Multi-level modulation of a 16.8-GHz class-E power amplifier with negative resistance enhanced power gain is demonstrated in a 130-nm CMOS process. The circuit achieves power gain of ~30 dB, and power-added efficiency (PAE) of 16% for the highest output power level of 6.8 dBm. The average efficiency for a random data pattern is ~8%. The circuit also exhibits 10-dBm saturated output power and ~22% maximum PAE. By realigning the highest output power level to the 10-dBm saturated output power, the efficiency can be improved. For a random data pattern, this PA should achieve ~2X higher efficiency than Class A PAs. The circuit supports seven amplitude levels for 400 Megabits per second (Mbps) data transmission. The multi-level output signal levels follow a square-root relation. The circuit including an address decoder occupies ~ 1.4 mm<sup>2</sup>.

Index Terms—Class-E, CMOS, multi-level modulation, power amplifiers.

# I. INTRODUCTION

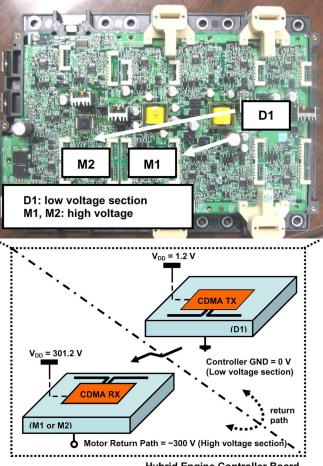

**H** YBRID electric vehicles (HEVs) with  $\sim 2$  times higher fuel efficiency are starting to be widely utilized [1]. Engine controller boards in HEVs have a high voltage (hundreds of volts) motor driver section (M1 and M2 in Fig. 1) and low voltage (less than 10 V) control section (D1 in Fig. 1). The low voltage section generates pulsewidth modulated signals for motor control and delivers them to the high voltage section. The floating potential of signal return path of high voltage/motor drive section can differ by several hundreds of volts from that for the low voltage section. Because of this, the signals are interfaced between the two sections using photo-couplers that isolate the return paths. The photo-couplers can support data transmission rate of  $\sim 1$  Mbps.

Wireless interconnection using two separate transceiver integrated circuits can also operate in the presence of large potential difference between the return paths. It can support the new higher data transmission rate target of 50-Mbps per channel.

K. K. O is with University of Florida, Gainesville, FL 32611 USA, and also with the University of Texas at Dallas, Richardson, TX 75080-3021 USA.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2010.2043879

Hybrid Engine Controller Board

Fig. 1. Hybrid engine controller board including a high voltage motor driver section and a low voltage control section.

On-chip antennas are integrated with the transmitter (TX) and receiver (RX) to accomplish the wireless communications between the controller and motor sections, as shown in Fig. 1. Expected transmission range is  $\sim 15$  cm. The lower die cost and elimination of wire traces on the PC board should also reduce cost. Because the system is placed in a metallic enclosure, the spectrum can be utilized free from the restrictions of government regulations. Code division multiple access (CDMA) is chosen for transmission from the low voltage section to high

Manuscript received September 09, 2009; revised January 14, 2010; accepted January 22, 2010. Current version published April 23, 2010. This paper was approved by Associate Editor Hooman Darabi. This work was supported by Toyota Motor Corporation and Toyota InfoTechnology Center Co., Ltd.

H.-T. Wu, R. Han, W. Lerdsitsomboon, and C. Cao are with University of Florida, Gainesville, FL 32611 USA (e-mail: hsinta.wu@gmail.com).

|              | Freq.    | Technology   | Classification | V <sub>DD</sub> | Small<br>Signal<br>Gain | P <sub>out</sub>               | PAE                           |

|--------------|----------|--------------|----------------|-----------------|-------------------------|--------------------------------|-------------------------------|

| [2]          | 18 GHz   | 0.13-µm CMOS | Class E        | 1.5 V           | > 30dB                  | 10.9 dBm                       | 23.5 %                        |

| [2]          | 20 GHz   | 0.13-µm CMOS | Class E        | 1.5 V           | 26 dB                   | 10.2 dBm                       | 20.5 %                        |

| [3]          | 17 GHz   | 0.13-µm CMOS | Class A        | 1.5 V           | 11 dB                   | 5 dBm<br>(@OP <sub>1dB</sub> ) | 2.4%<br>(@OP <sub>1dB</sub> ) |

| [4]          | 17 GHz   | 0.13-µm CMOS | Class B        | 1.5 V           | 14.5 dB                 | 17.1 dBm                       | 9.3 %                         |

| [5]          | 24 GHz   | 0.18-µm CMOS | N/A            | 2.8 V           | 7 dB                    | 14.5 dBm                       | 5~6 %                         |

| This<br>work | 16.8 GHz | 0.13-µm CMOS | Class E        | 1.5 V           | ~ 30 dB                 | 10 dBm                         | < 22 %                        |

TABLE I

COMPARISONS OF POWER AMPLIFIERS OPERATING NEAR 20 GHz

voltage section to mitigate the effects of multi-path rich environment in the hybrid engine controller board and to simplify the transmitter design. The receiver at motor side amplitude detects and decodes the CDMA signal.

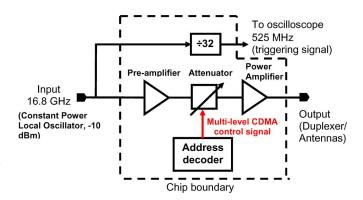

A multi-level (seven) power amplifier (PA) is a key block for implementing the CDMA transmitter. This PA takes constant power 16.8-GHz local oscillator signal as the input and generates modulated output. Since a form of multiple level amplitude shift keying (ASK) is used for CDMA, an obvious topology choice for a PA is a linear type. Instead, this paper reports use of a nonlinear class-E PA with negative resistance enhanced output power which is typically used for constant envelope modulation systems for improved power efficiency [2]–[5] (Table I). The PA efficiency of this work is comparable to PAs operating at similar frequencies. Because of the high data rate (400 Mbps), supply modulation could not be used and weighted attenuator switching is selected for level control. The class-E PA operates at 16.8 GHz and fabricated in a 130-nm CMOS process.

## II. CIRCUIT DESIGN

In this section, design considerations are discussed. In Section II-A, methods for implementing the multi-levels are described. The digital control scheme is described in II-B. The design challenges and solutions for improving the switching performance are discussed in Section II-C. Finally, issues for controlling the self oscillation resulting from the use of negative resistance enhanced power gain are presented in Section II-D.

#### A. Multiple Level Implementation

There are several ways to realize multi-level amplitude modulation at the PA output. One is to modulate the supply voltage to control output power of PA [6], [7]. The PA can be linear or nonlinear [8]–[11]. Supply modulation requires a dc-dc converter to implement a dynamic voltage supply. The converter significantly increases the chip area. The required chip rate of 400 Mchips/sec for the wireless interconnect system instead of hundreds of kHz or 10's of MHz for cellular applications makes use of a supply modulated power amplifier particularly difficult. It is also sensitive to supply variations and requires a feedback loop for tracking and adjusting the PA envelope.

The second way for realizing multi-level amplitude modulation is to use a current-steering technique [12] to modulate the

Fig. 2. Block diagram of multiple level amplitude modulated power amplifier.

gate bias of pre-drivers. A similar idea was used to lower quiescent current at low output power to improve PA efficiency (adaptive bias control) [10], [11]. However, based on simulations, fall times are long and precise gain control is difficult by adjusting only gate bias without closed-loop control. The closed-loop control will complicate the design. Adaptive closed-loop bias control for WCDMA applications [13], [14] uses a power sensor to precisely control the gate bias of PA stage. Use of this is expected to be challenging for the desired data rate of 400 Mbps. A simpler approach is required for a PA operating at the desired carrier frequency of 16.8 GHz, and to achieve sufficient response time.

Another approach to multi-level modulate a PA is to incorporate switchable attenuators. As shown in Fig. 2, the attenuators can be placed at the signal path to adjust the signal level into the PA stage [15], [16] as well as the negative resistance seen by the PA. Each level control is accomplished by turning on/off appropriate combinations of attenuators, which can modulate the signal swing at the gate of the fourth pre-driver and implement the required multi-level control signals. The truth table for the coding scheme is shown in Table II. Consequently, the multi-level signals for 400 Mbps data can be formed at the gate of PA stage as well as its output. Since the switched capacitances of attenuators are smaller, the PA can readily support the modulation for the required data rate of 400 Mbps.

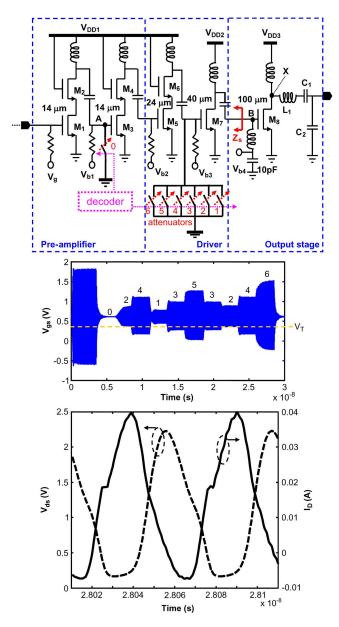

Fig. 3(a) shows the schematic of single-ended CDMA PA. It includes four pre-drivers and a PA stage. The first three predrivers are implemented using cascode amplifiers and the fourth pre-driver is a common-source amplifier. The pre-drivers are designed to achieve high voltage gain, while the last PA stage

| "additive/subtractive" | att_0                        | att_1 | att_2 | att_3 | att_4              | att_5 | att_6 |  |

|------------------------|------------------------------|-------|-------|-------|--------------------|-------|-------|--|

| Level 6                | 0                            | 0     | 0     | 0     | 0                  | 0     | 1     |  |

| Level 5                | 0                            | 0     | 0     | 0     | 0                  | 1     | 1     |  |

| Level 4                | 0                            | 0     | 0     | 0     | 1                  | 1     | 1     |  |

| Level 3                | 0                            | 0     | 0     | 1     | 1                  | 1     | 1     |  |

| Level 2                | 0                            | 0     | 1     | 1     | 1                  | 1     | 1     |  |

| Level 1                | 0                            | 1     | 1     | 1     | 1                  | 1     | 1     |  |

| Level 0                | 1                            | 1     | 1     | 1     | 1                  | 1     | 1     |  |

|                        |                              |       |       |       |                    |       |       |  |

|                        | Ideal ratio at TX side       |       |       |       | After RX detection |       |       |  |

| Level 2 / Level 1      | $\sqrt{2}$                   |       |       |       | 2                  |       |       |  |

| Level 3 / Level 1      | $\sqrt{3}$                   |       |       |       | 3                  |       |       |  |

| Level 4 / Level 1      | $\sqrt{4}$                   |       |       |       | 4                  |       |       |  |

| Level 5 / Level 1      | $\sqrt{5}$                   |       |       |       | 5                  |       |       |  |

| Level 6 / Level 1      | Level 6 / Level 1 $\sqrt{6}$ |       |       |       | 6                  |       |       |  |

TABLE II TRUTH TABLE OF ADDITIVE/SUBTRACTIVE CODING SCHEME, AND THE RATIO BETWEEN LEVELS AT TX SIDE AND AFTER RX DETECTION

is designed for maximizing output power and efficiency. The common-source fourth pre-driver allows larger output voltage swing.

To minimize power consumption and increase efficiency, the values of output matching components  $[C_1, C_2, and L_1 in Fig. 3(a)]$  are chosen such that the drain current of  $M_8$  should be low when  $V_x$  (voltage across the drain and source of  $M_8$ ) is high [17]. The simulated threshold voltage of transistor in the 130-nm process is 0.38 V. The gate bias of PA stage is set to 0.6 V. Due to the large voltage swing at the gate of  $M_8$ , the transistor operates in mostly the switching mode for levels 3–6. As discussed, the attenuator setting at the gate of pre-driver is used to set the signal level at the gate of the fourth pre-driver. Varying the over drive changes the duration in switching mode, and output level.

Fig. 3(b) shows a simulated output waveform. As expected, the voltage ( $V_{ds}$ ) and current ( $I_D$ ) waveforms at the drain of  $M_8$  are out of phase [shown in Fig. 3(c)], which reduces the power dissipation and improves the efficiency compared to using a PA with conduction angle of 360 degree. Assuming equal probability for output levels (1–6), the simulated average PAE of class E PA is ~14% instead of ~6.6% for a class A PA. The PAE calculation includes all the pre-driver stages power consumption. Regardless of the design for output matching network to make  $V_{ds}$  and  $I_D$  of  $M_8$  to be out of phase, the multi-level PA does not operate in the pure Class-E mode for levels 3 to 6. This is mainly due to the difficulty for providing a perfect square waveform at the gate of PA stage at the required high operating frequencies. The maximum  $V_{ds}$  can only achieve ~2X  $V_{DD}$  [shown in Fig. 3(c)] instead of the ideal value of 3.56X  $V_{DD}$ .

As shown in Fig. 3(a), there are seven attenuators with varying transistor sizes to set the seven PA output levels. The gate node of each attenuator is connected to a decoder output. There are six attenuators connected at the gate of the fourth pre-driver stage. There is also an attenuator connected at the gate of second stage. The decoder provides control pulses to turn on or off appropriate combinations of attenuators. Since the signal swing and transistor sizes at the second stage is smaller than that at the fourth stage, the attenuator size for level 0 can be made smaller by placing at an earlier pre-amplifier

stage. This decreases the transistor size needed to control level 0, which reduces the loading in the signal path and drivability requirement for the decoder. The attenuators are simple nMOS switches. For better level tracking with process variation, the switches are formed using a varying number of parallel connected unit cells (0.25  $\mu$ m/0.12  $\mu$ m). Level 6 requires a unit cell attenuator.

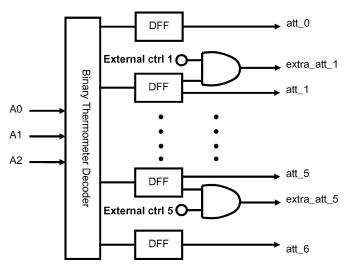

## B. Digital Control Scheme

A thermometer decoding (additive/subtractive coding scheme) is selected over simple decoding scheme in which one attenuator is turned on while another one is turned off to reduce glitches during transitions and to suppress the self oscillation. The truth table is shown in Table II. For the additive/subtractive coding scheme, all the attenuators are turned on to set level 0. On the other hand, for level 6, only one attenuator is turned on. The ratios of numbers of turned on switches between level N and level 1 (N = 2, 3, 4, 5 6) implement the square-root function (Table II) to accommodate the squaring in a receiver using a diode detector [18], [19]. Consequently, receiver outputs with a roughly constant voltage step are generated. Lastly, for post fabrication digital calibration of the level ratios (att\_1 to att\_5), five small switches consisting of a varying number of parallel connected unit cells  $(0.25 \ \mu m/0.12 \ \mu m)$  with AND gates are added as shown in Fig. 4. D-flip-flops added at the output of binary thermometer decoder help synchronize decoder outputs.

## C. Rise and Fall Times

Another design requirement is controlling the rise and fall times of output envelope. The target for rise and fall times of an envelope is ~10% or ~250 ps. These transition times are determined by the *RC* time constants associated with switching the attenuators at the gates for second and fourth stages. Since the additive/subtractive coding scheme has been chosen, the following discussion is limited for this coding case.

For this coding scheme, levels are changed by turning on additional necessary attenuators or turning off some necessary attenuators instead of turning all off and turning on a new set. For example, for the level 4 to level 6 transition, the extra switches needed to be turned off are switches 4 and 5 only as can be seen

Fig. 3. (a) Schematic of a single-ended five-stage class-E CMOS power amplifier. (b) Simulated  $\rm V_{gs}$  waveform at the gate of PA transistor [node B in Fig. 3(a)]. (c) Simulated waveforms of  $\rm V_{ds}$  and  $\rm I_D$  of the PA transistor [node X in Fig. 3(a)].

from Table II. The sizes of switches (attenuators) for the additive/subtractive coding scheme are shown in Table III. That means the capacitance required to be switched is mainly from switches 4 and 5. The smaller switched capacitance leads to shorter rise and fall times. The switch sizes are chosen to be as small as possible to keep reducing rise and fall times. Meanwhile, it has to be sufficiently large to provide the necessary attenuation and implement the square-root function.

Presently, longer transition times are the rise times for level 0 to level N (N = 1–6) which are largely determined by the gate bias resistor at the second pre-driver stage. The gate bias resistor is 5 k $\Omega$ . This value is chosen to prevent the loading of 16.8-GHz carrier signal. However, this increases the *RC* time constant of the equivalent network at the gate of second pre-driver, thus the rise and fall times. Varying the attenuator settings change the

Fig. 4. Decoder block diagram with external bias control for AND gates to turn on extra attenuators for post fabrication digital calibration.

TABLE III SWITCH SIZES FOR THE ADDITIVE/SUBTRACTIVE CODING SCHEMES (THE SWITCH (ATTENUATOR) SIZES ARE FOR THE SINGLE-ENDED PA.)

| additive/subtractive | Switch size                                                               |  |  |

|----------------------|---------------------------------------------------------------------------|--|--|

| att_6                | $(0.25 \mu\text{m} / 120 \text{nm}) \ge 1 = 0.25 \mu\text{m}$ width       |  |  |

| att_5                | $(0.25 \mu\text{m} / 120 \text{nm}) \ge 3 = 0.75 \mu\text{m}$ width       |  |  |

| att_4                | $(0.25 \mu\text{m} / 120 \text{nm}) \ge 5 = 1.25 \mu\text{m}$ width       |  |  |

| att_3                | $(0.25 \mu\text{m} / 120 \text{nm}) \ge 6 = 1.5 \mu\text{m}$ width        |  |  |

| att_2                | $(0.25 \mu\text{m} / 120 \text{nm}) \ge 6 = 1.5 \cdot \mu\text{m}$ width  |  |  |

| att_1                | $(0.25 \mu\text{m} / 120 \text{nm}) \ge 9 = 2.25 \cdot \mu\text{m}$ width |  |  |

| att_0                | $(0.25 \mu\text{m} / 120 \text{nm}) \ge 36 = 9 - \mu\text{m}$ width       |  |  |

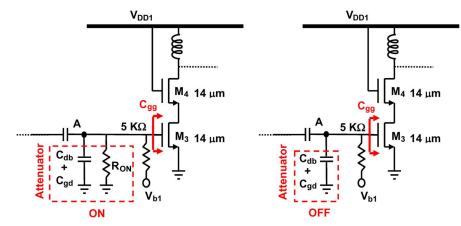

equivalent *RC* network as shown in Fig. 5. When the switch is OFF, the parasitic capacitance of switch added to node A is  $(C_{db} + C_{gd})$ . When the switch is ON, the parasitic capacitance is still around  $(C_{db} + C_{gd})$ . However, the on resistance of the switch is much smaller compared to the 5-k $\Omega$  bias resistor. Therefore, the equivalent resistance  $(R_{eq})$  is dominated by the on resistance of attenuator switch. The total equivalent capacitance at node A is relatively constant, which is roughly the sum of  $C_{db}$  and  $C_{gd}$  of attenuator,  $C_{gg}$  of the pre-driver, and other parasitic capacitance (Fig. 5). These are lumped and represented as  $C_{eq}$ . During a transition from level 0 to level N (N = 1–6), the equivalent resistance changes from several tens of ohms to 5 k $\Omega$ . The rise time is ~  $2R_{eq}C_{eq}$  and the largest when the attenuator is off.

# D. Self Oscillation Control

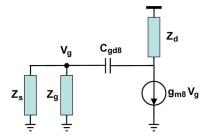

As mentioned earlier, the bias of class-E PA  $(V_{b4})$  is applied through an inductor. The inductor along with  $C_{gd}$  of the last PA stage can generate negative resistance, which increases the PA gain and efficiency [2], [20], [21]. However, a concern is the self oscillation at the last PA stage that can increase the level zero output power. The self oscillation must be properly controlled to set the required lower level signals. Fig. 6 shows the small-signal model of the last PA stage [2]. Turning on and off of varying combinations of attenuators at the input of the fourth pre-driver stage modifies the impedance looking back toward the drain of stage ( $Z_s$  in Fig. 3(a)). Use of a common-

Fig. 5. Lumped circuit models with the attenuator switched ON and OFF. The rise and fall times depend on the *RC* time constant of equivalent network at the gate node of second pre-driver [Node A in Fig. 3(a)].

Fig. 6. Small-signal model of the last PA stage (common-source amplifier).  $Z_s$  is the impedance looking back toward the fourth pre-driver stage.  $Z_g$  is the impedance of the bias inductor.  $Z_d$  is the drain load inductor.

source fourth pre-driver stage because of relatively high  $S_{12}$ , increases the impact of input termination to the output impedance of stage,  $Z_s$ .

The open loop gain of PA stage is

$$T(s) = -g_{m8} \left\{ Z_d / / \left[ (Z_g / / Z_s) + \frac{1}{sC_{gd8}} \right] \right\}$$

•  $\frac{(Z_g / / Z_s)}{(Z_g / / Z_s) + \frac{1}{sC_{gd8}}}$  (1)

$$Z_s \propto \frac{1}{g_{m7}} \left( 1 + \frac{1}{sC_{gd7} \bullet \left(Z_{att}//Z_{gs7}\right)} \right) \tag{2}$$

$Z_{\rm att}$  represents the impedance associated with the attenuators at the gate of the fourth pre-driver stage.  $Z_{\rm gs7},\,C_{\rm gd7}$  and  $g_{\rm m7}$  are the impedance of gate to source capacitance, gate to drain capacitance and transconductance for transistor M7, respectively. When attenuators are turned on  $Z_{\rm att}$  decreases and the real part of  $Z_{\rm s}$  increases. This in turn lowers the open loop gain,  $|T({\rm s})|$  and modifies the phase. The oscillation starts when the loop gain is greater than 1 and the phase is equal to 360 degree [2]. When all the attenuators are turned on to set level 0, the oscillation is suppressed.

The circuit is near this oscillation condition without any 16.8-GHz RF sinusoidal input and all the attenuators turned off. The circuit oscillates at  $\sim 21$  GHz. With an RF input greater than -35 dBm, the self oscillation is suppressed. In the frequency domain, only one single desired frequency peak is observed. For level 0 when all the attenuators are on, the self os-

Fig. 7. PA measurement setups for frequency and time domain characterization.

cillation is suppressed to provide a near zero amplitude output. In Section III, experimental verification of this is presented.

#### **III. MEASUREMENT RESULTS**

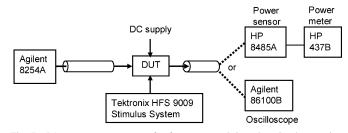

Fig. 7 shows the large signal measurement setup for the frequency and time domain characterization. For frequency domain measurements, the output is connected to a power meter through an HP8485A power sensor. For time domain measurements, the output is connected to an Agilent 86100B wide bandwidth oscilloscope. To characterize the time domain response of multi-level PA, an on-chip divide-by-32 block is included to generate 525-MHz signal for oscilloscope triggering. The three address decoder inputs are fed from a Tektronix HFS 9009 Stimulus System, which can provide 4 synchronized signals up to 400 MHz. The clock frequency is 400 MHz and the frequency of inputs for the address decoder is 200 MHz. The inputs can be randomly chosen using the stimulus system. For illustration, a randomly chosen pattern (0241353246) is used for the dynamic measurements.

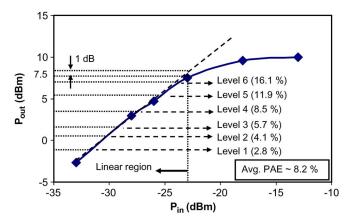

At 1.5-V supply voltage for the driver stages and 1.2-V supply voltage for the PA stage, Fig. 8 shows the single-ended PA is able to achieve power gain of ~30 dB, 10-dBm saturated power and ~22-% maximum PAE at 16.8 GHz while drawing 30.5 mA and consuming 45.8 mW. The drain efficiency of last PA stage is ~38%. Fig. 8 shows that it is possible to provide sufficient linear power. The output  $P_{1 dB}$  ( $OP_{1 dB}$ ) is ~7.5 dBm, which corresponds to ~10.5-dBm  $OP_{1 dB}$  for a differential PA structure. In actual operation, the PA will operate below the  $OP_{1 dB}$  point much of the time to implement the multi-level amplitude modulation.

Fig. 8. Output power of single ended PA versus input power at  $V_{DD} = 1.5 \text{ V}$  for the driver stages and 1.2-V supply for the PA stage.  $OP_{1 \text{ dB}}$  is 7.5 dBm (with all the attenuators off).

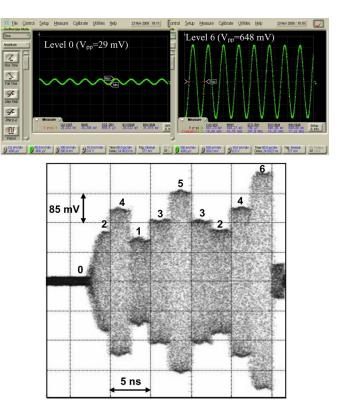

By applying constant DC inputs to the address decoder, static level test can be performed. Fig. 9(a) shows the static time domain measurement results for level 0 and level 6. The input power level to the PA is  $\sim -10$  dBm. The frequency of output sinusoidal waveform is 16.8 GHz, which is the same as the PA input frequency. When the PA output is connected to a spectrum analyzer, no other peaks except the desired 16.8-GHz peak are seen at all output levels. The output power at level 0 is approximately -20 dBm. This means the self oscillation is suppressed for level 0. Level 2 to level 5 measurement results are summarized in Table IV. After de-embedding the probe and cable losses, the corresponding output power for level 6 is  $\sim$ 7 dBm, which means the single-ended PA operates close to the  $OP_{1 \text{ dB}}$ point. This is consistent with the original design. When a differential PA is used,  $OP_{1 dB}$  will be ~10 dBm. The current consumption for each level is also summarized in Table IV. The PAE performance for level 1 to level 6 is marked in Fig. 8 with the average efficiency of  $\sim 8\%$ . By realigning the highest output power level to the 10-dBm saturated output power, the efficiency can be further improved. By using a differential PA integrated in the CDMA TX chain, expected link margin can be around 20 dB assuming RX noise figure of 8 dB, bandwidth of 50 MHz (one of eight channels), minimum signal to noise ratio of 14.5 dB, and propagation/antenna loss of 55 dB at 15-cm separation with a metal cover [22].

Fig. 9(b) is the dynamic measurement results for the chosen random pattern (0241353246). The rise and fall times of the 3 inputs and clock are set to 200 ps, which is the minimum for the stimulus system. There are built-in inverter buffer chains on chip for squaring the input waveform. The PA output is AC-coupled. Because of this, the waveform in Fig. 9(b) is symmetrical with respect to the time axis. Each level has a period of ~2.5 ns to support the 400-Mbps data rate. Table IV also summarizes the measurement results of level ratio between level N (N = 6, 5, 4, 3, 2) and level 1, and the percent error is compared with the ideal. The measured rise and fall times for some of the transitions are listed in Table V.

The level 0 output voltage is only 31 mV which should be acceptable. The 19-dB difference between level 0 and level 1 is sufficiently large for the ASK receiver to distinguish between

Fig. 9. (a) Time domain measurement results for static level 0 and level 6 operating at 16.8 GHz. (The value of  $\rm V_{pp}$  is before de-embedding cable loss). (b) Time domain measurement results for a dynamic input pattern of 0241353246.

the 2 levels. More importantly, the frequency of signal is the same as that for the input of 16.8 GHz, which indicates that this is due to the feed through of input signal. As explained in Section II, self oscillation can occur at the last PA stage, it can be suppressed by properly setting the impedance  $Z_s$  [Fig. 3(a)]. This has been experimentally verified. The maximum percent error of the level ratio is  $\sim 16\%$  (level 3 to level 1). The error can be fixed by re-tuning the attenuator sizes. A switch (attenuator) array using an even smaller unit cell will be useful for post fabrication tuning to improve the level ratio accuracy. From the measurements, the worst rise time is  $\sim$ 800 ps (level 0 to level 2 transition), which is largely determined by the gate bias resistor at the second pre-driver stage as discussed in Section II. This rise time can be decreased by lowering the bias resistor at the gate of second pre-amplifier to 0.8 k $\Omega$ . This however reduces the signal level at the input of second stage and another amplification stage is needed following the second stage to maintain the output power of PA. This in conjunction with decreasing the level-0 switch size reduces the rise time (level 0 to level 2) to  $\sim$ 300 ps in simulations. The rise and fall times for other level transitions are  $\sim 200$  ps, which are shorter than the original target.

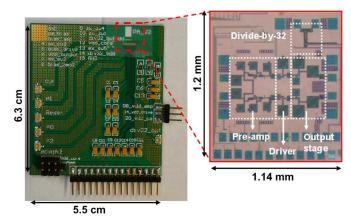

Fig. 10 shows the die micrograph and the test printed circuit board (PCB). The differential class-E PA with an address decoder and bond pads occupies  $\sim 1.4 \text{ mm}^2$ . The circuit was measured on a printed circuit board to improve the reliability of measurements. However, due to the bonding scenario of the test chip on a printed circuit board, only the single-ended measurements mentioned earlier were made.

|                              |  | V <sub>peak</sub> (mV) | Powe  | r (dBm)   | Current (mA) |  |

|------------------------------|--|------------------------|-------|-----------|--------------|--|

| Level 0                      |  | 31.0                   | -20.2 |           |              |  |

| Level 1                      |  | 268.2                  | -1.4  |           | 19.6         |  |

| Level 2                      |  | 331.5                  | 0.4   |           | 20.2         |  |

| Level 3                      |  | 390.4                  | 1.8   |           | 20.3         |  |

| Level 4                      |  | 478.6                  | 3.6   |           | 20.4         |  |

| Level 5                      |  | 577.4                  | 5.2   |           | 21.2         |  |

| Level 6                      |  | 692.6                  | 6.8   |           | 22.5         |  |

| Ideal ratio                  |  | Measured ratio results |       | Error (%) |              |  |

| Level 2 / Level 1 $\sqrt{2}$ |  | 1.24                   |       | -12.3     |              |  |

| Level 3 / Level 1 $\sqrt{3}$ |  | 1.45                   |       | -16.0     |              |  |

| Level 4 / Level 1 $\sqrt{4}$ |  | 1.79                   |       | -10.8     |              |  |

| Level 5 / Level 1 $\sqrt{5}$ |  | 2.15                   |       | -3.9      |              |  |

| Level 6 / Level 1 $\sqrt{6}$ |  | 2.58                   |       | 5.3       |              |  |

TABLE IV

MEASUREMENT RESULTS SUMMARY OF STATIC CASE (ADDITIVE/SUBTRACTIVE CODING)

TABLE V MEASUREMENT RESULTS SUMMARY OF RISE AND FALL TIMES OF SOME LEVEL TRANSITIONS

| Transitions       | Rise or Fall time (ps) |

|-------------------|------------------------|

| Level 0 – level 2 | 830                    |

| Level 2 – level 3 | 180                    |

| Level 3 – level 1 | 180                    |

| Level 1 – level 3 | 180                    |

| Level 3 – level 5 | 240                    |

| Level 5 – level 3 | 180                    |

| Level 3 – level 2 | 180                    |

| Level 2 – level 4 | 180                    |

| Level 4 – level 6 | 300                    |

| Level 6 – level 0 | 360                    |

| Level 0 – level 6 | 660                    |

| Level 4 – level 1 | 240                    |

| Level 6 – level 2 | 180                    |

Fig. 10. Test printed circuit board  $(6.3 \times 5.5 \text{ cm}^2)$ . Die micrograph of the differential multi-level power amplifier  $(1.14 \times 1.2 \text{ mm}^2)$ .

# IV. CONCLUSION

A technique to support 400-Mbps data rate using multiple-level amplitude modulation of a nonlinear power amplifier with negative resistance enhanced power gain is proposed and demonstrated in a 16.8-GHz seven-level amplitude modulated class-E PA. This is accomplished by adding attenuators that both reduce the signal level as well as that change the impedance seen by the PA stage for suppression of self-oscillation at low output power levels. The single-ended PA fabricated in a 130-nm foundry logic CMOS process achieves power gain of  $\sim$ 30 dB, and power-added efficiency (PAE) of 16% for the highest output power level of 6.8 dBm. The average efficiency for a random data pattern is  $\sim$ 8%. The circuit also exhibits 10-dBm saturated output power and  $\sim$ 22% maximum PAE while consuming 45.8 mW. By realigning the highest output power level to the 10-dBm saturated output power, the efficiency can be improved. The drain efficiency of last PA stage is  $\sim$ 38%. Lastly, this work suggests that by using a combination of switched attenuators and a nonlinear Class-E PA, power efficiency of multiple-level amplitude modulated PAs can be improved over linear PAs.

#### REFERENCES

- A. Kawahashi, "A new-generation hybrid electric vehicle and its supporting power semiconductor devices," in *IEEE Power Semiconductor Devices and ICs Symp. Dig. Tech. Papers*, May 24–27, 2004, pp. 23–29.

- [2] C. Cao, H.-F. Xu, Y. Su, and K. K. O, "An 18-GHz, 10.9-dBm fully-integrated power amplifier with 23.5% PAE in 130-nm CMOS," in *Proc. ESSCIRC*, Sep. 2005, pp. 137–140.

- [3] R. Thuringer, M. Tiebout, W. Simburger, C. Kienmayer, and A. L. Scholtz, "A 17 GHz linear 50 Ω output driver in 0.12 µm standard CMOS," in *IEEE Radio Frequency Integrated Circuits (RFIC) Symp. Dig.*, Jun. 2003, pp. 207–210.

- [4] A. V. Vasylyev, P. Weger, W. Bakalski, and W. Simbuerger, "17-GHz 50–60 mW power amplifiers in 0.13-μm standard CMOS," *IEEE Microw. Wireless Compon. Lett.*, vol. 16, no. 1, pp. 37–39, Jan. 2006.

- [5] A. Komijani, A. Natarajan, and A. Hajimiri, "A 24-GHz, +14.5-dBm fully integrated power amplifier in 0.18-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 40, no. 9, pp. 1901–1908, Sep. 2005.

- [6] F. H. Raab, B. E. Sigmon, R. G. Myers, and R. M. Jackson, "L-band transmitter using Kahn EER technique," *IEEE Trans. Microw. Theory Tech.*, vol. 46, no. 12, pp. 2220–2225, Dec. 1998.

- [7] D. Su and W. McFarland, "An IC for linearizing RF power amplifiers using envelope elimination and restoration," *IEEE J. Solid-State Circuits*, vol. 33, no. 12, pp. 2252–2258, Dec. 1998.

- [8] P. Midya, M. Greuel, and P. T. Krein, "Sensorless current mode control—An observer based technique for DC-DC converters," in *Proc.* 28th Annual IEEE Power Electronics Specialists Conf., 1997, vol. 1, pp. 197–202.

- [9] G. Hanington, P. Chen, P. M. Asbeck, and L. E. Larson, "High-efficiency power amplifier using dynamic power-supply voltage for CDMA applications," *IEEE Trans. Microw. Theory Tech.*, vol. 47, no. 8, pp. 1471–1476, Aug. 1999.

- [10] P. Midya, K. Haddad, L. Connell, S. Bergstedt, and B. Roeckner, "Tracking power converter for supply modulation of RF power amplifier," in *Proc. 32nd Annual IEEE Power Electronics Specialists Conf.*, 2001, vol. 3, pp. 1540–1545.

- [11] B. Sahu and G. A. Rincon-Mora, "A high-efficiency linear RF power amplifier with a power-tracking dynamically adaptive buck-boost supply," *IEEE Trans. Microw. Theory Tech.*, vol. 52, no. 1, pt. 1, pp. 112–120, Jan. 2004.

- [12] A. S. Sedra and K. C. Smith, *Microelectronic Circuits*, 4th ed. Oxford, U.K.: Oxford University Press, 1997.

- [13] Y. S. Noh and C. S. Park, "An intelligent power amplifier MMIC using a new adaptive bias control circuit for W-CDMA applications," *IEEE J. Solid-State Circuits*, vol. 39, no. 6, pp. 967–970, Jun. 2004.

- [14] B. Sahu and G. A. Rincon-Mora, "A high efficiency WCDMA RF power amplifier with adaptive, dual-mode buck-boost supply and biascurrent control," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 3, pp. 238–240, Mar. 2007.

- [15] R. B. Staszewski, J. L. Wallberg, S. Rezeq, C.-M. Hung, O. E. Eliezer, S. K. Vemulapalli, C. Fernando, K. Maggio, R. Staszewski, N. Barton, M.-C. Lee, P. Cruise, M. Entezari, K. Muhammad, and D. Leipold, "All-digital PLL and transmitter for mobile phones," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2469–2482, Dec. 2005.

- [16] A. Kavousian, D. K. Su, and B. A. Wooley, "A digitally modulated polar CMOS PA with 20 MHz signal BW," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2007, pp. 78–588.

- [17] N. O. Sokal and A. D. Sokal, "Class E-A new class of high efficiency tuned single-ended switching power amplifier," *IEEE J. Solid-State Circuits*, vol. 10, no. 3, pp. 168–176, Jun. 1975.

- [18] S. Sankaran and K. K. O, "Schottky barrier diides for millimeter wave detection in a foundry CMOS process," *IEEE Electron Device Lett.*, vol. 26, no. 7, pp. 492–494, Jul. 2005.

- [19] S. Sankaran, K. Oh, H.-T. Wu, and K. K. O, "Wireless interconnection within a hybrid engine controller board," in *Proc. CICC*, Sep. 2008, pp. 149–152.

- [20] K.-C. Tsai and P. R. Gray, "A 1.9-GHz, 1-W CMOS class-E power amplifier for wireless communications," *IEEE J. Solid-State Circuits*, vol. 34, no. 7, pp. 962–970, Jul. 1999.

- [21] K. L. R. Mertens and M. S. J. Steyaert, "A 700-MHz 1-W fully differential CMOS class-E power amplifier," *IEEE J. Solid-State Circuits*, vol. 37, no. 2, pp. 137–141, Feb. 2002.

- [22] H.-T. Wu, "Transmitter for wireless inter-chip data communications," Ph.D. dissertation, Univ. of Florida, Gainesville, FL, 2009.

His main research interests include microwave/RF ICs design and electromagnetic wave propagation.

**Ruonan Han** was born in Huhhot, China, in 1984. He received the B.S. degree in microelectronics from Fudan University, Shanghai, China, in 2007, and the M.S. degree in electrical engineering from the University of Florida, Gainesville, in 2009. He is currently working toward the Ph.D. degree at the University of Florida, where he is a research assistant in the Silicon Microwave Integrated Circuits and Systems Research Group (SIMICS).

His current research is focused on high- $f_T$ Schottky-barrier diode in CMOS process, and its application in millimeter-wave and submillimeter-wave detector design. He is also conducting research on flicker noise and low-noise analog circuits.

Wuttichai Lerdsitsomboon received the B.Eng. degree in electrical engineering from Chulalongkorn University, Bangkok, Thailand, in 2003. He received the M.S. degree in electrical and computer engineering from the University of Florida, Gainesville, in 2006, and is currently pursuing the Ph.D. degree in the same department.

His current research interests are low-power RFIC and analog circuit designs in CMOS technology.

In August 2006, he joined the Wireless Products Division of Silicon Labs, Austin, TX, as a design engineer. Currently, he is a Member of Technical Staff with MediaTek USA Inc., Austin, TX. His research interests include CMOS multi-mode transceivers and

frequency synthesizers.

Kenneth K. O received the S.B, S.M, and Ph.D. degrees in electrical engineering and computer science from the Massachusetts Institute of Technology, Cambridge, in 1984, 1984, and 1989, respectively.

From 1989 to 1994, he worked at Analog Devices Inc. developing submicron CMOS processes for mixed-signal applications and high-speed bipolar and BiCMOS processes for RF and mixed-signal applications. He was a Professor at the University of Florida, Gainesville, from 1994 to 2009. Currently, he is the Texas Instruments Inc. Distinguished Chair

Professor in Analog Circuits and Systems at the University of Texas, Dallas, and the Director of SRC Texas Analog Center of Excellence. His research group (Silicon Microwave Integrated Circuits and Systems Research Group) is developing circuits and components required to implement analog and digital systems operating between 1 GHz and 1 THz using silicon IC technologies. He has authored or coauthored about 180 journal and conference publications, and holds ten patents.

Dr. O served as an associate editor for IEEE TRANSACTIONS ON ELECTRON DEVICES from 1999 to 2001. He also served as the publication chairman of the 1999 International Electron Device Meeting. He was elected to the IEEE Solid-State Circuits Society Adcom in 2008. He was the general chair of the 2001 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM). He received the 1996 NSF Early Career Development Award and 2003 UF Ph.D./Mentor Award. He was also a UF Research Foundation Professor from 2004 to 2007.